## **Problem Statement:**

- Develop a process to ulletfabricate digital ASICs through the MPW Shuttle program

- Create a bring-up plan for chip fabrications

- Design a SHA1 hashing accelerator for the MPW shuttle submission

## **Intended Use Cases:**

- Provide undergraduate students at Iowa State with a means to fabricate ASICs

- Reinforce hands-on ulletoriented research pedagogy for hardware design senior design teams

## **Design Approach:**

# **Digital ASIC Fabrication**

Dawood Ghauri, Constantine Mantas, Soma Szabo, Courtney Violett Client: Dr. Henry Duwe

### **Technical Details:**

$\bullet$

ullet

$\bullet$

•

Used Windows Subsystem for Linux (WSL) for

**Caravel User environment**

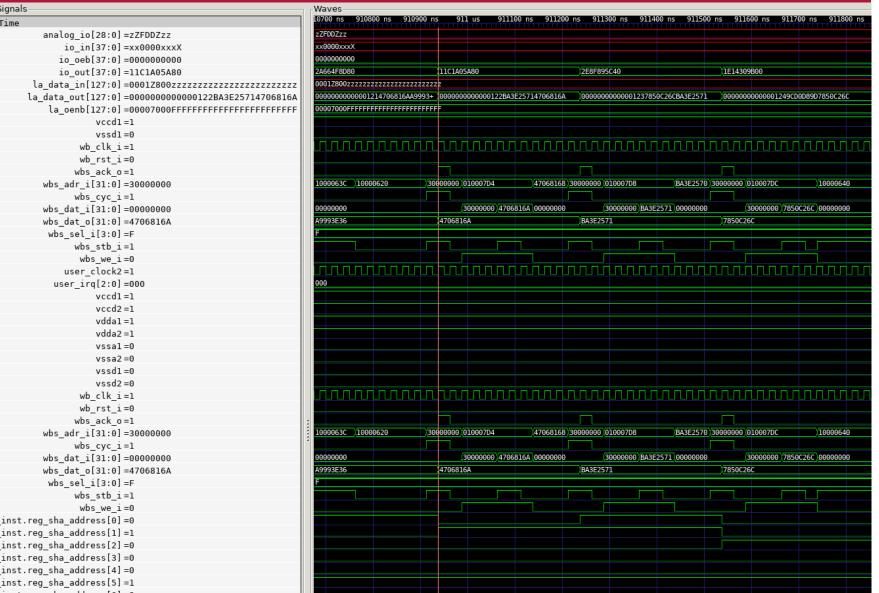

- Created Verilog testbenches to test functional • units

- Created firmware test cases in C running on SoC  $\bullet$

- Probed signals using logic analyzer subcomponent

- Utilized Verilog within Efabless framework to implement our design

#### **Testing**:

Multiple testbenches with various inputs like

## **Design Requirements:**

- Design passes MPW precheck and tapeout

- RTL and GL chip simulation ullettestbenches pass

- Design functions as a • hardware accelerated SHA1 hasher (modified from Bitcoin miner)

- Simulate unit tests in the • caravel simulation environment

- Design hardens through ullet**OpenLANE**

- Power/timing constraints ۲ are met after hardening design

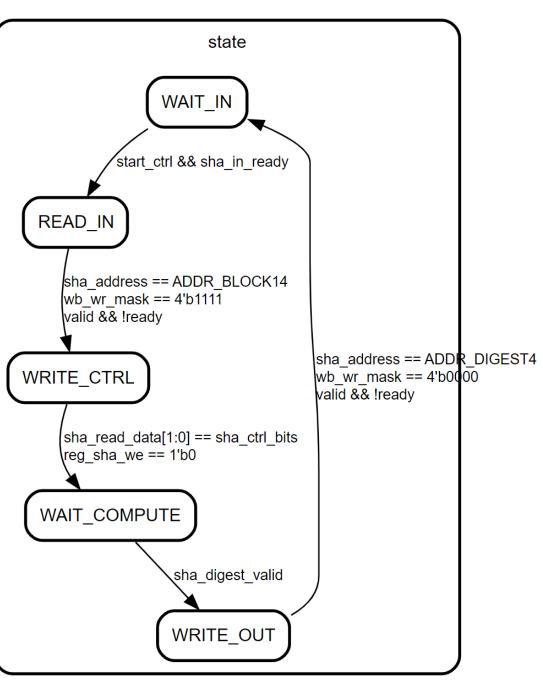

State Machine Design

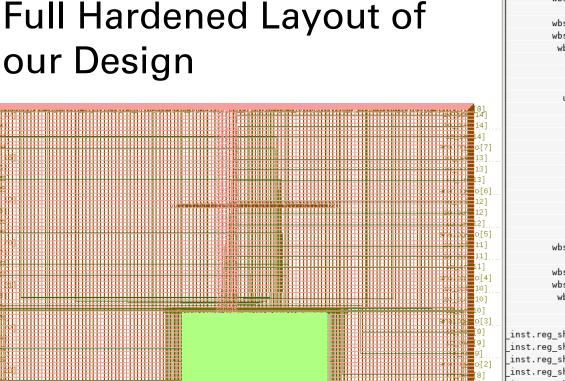

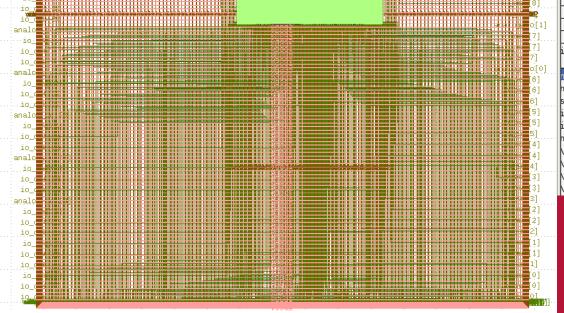

• Full Hardened Layout of our Design

'abc'

- Correct output on 'wbs\_dat\_o'

- Simulations passed RTL and GL tests

- Consisted of C & Verilog code

- Logic analyzer ports used as probes to ensure data in/out are correct

- eFabless submission process for precheck and tapeout

- Multiple trials of hardening so design physically

### fits & functions in user project area

- The IP integrated has no security risk

- **IEEE Standard VITAL ASIC** • (Application Specific **Integrated Circuit**) **Modeling Specification -**Designed an ASIC using a modeling standard allow us to clearly communicate our design to other engineers.

- **IEEE Standard for** Integrated Circuit (IC) **Open Library Architecture** (OLA)- Useful as it covers ways for integrated circuit designers to analyze chip timing & power consistently across a broad set of electric design automation (EDA) applications.

## **Project Resources:** Budget – \$0

Main security concern is  $\bullet$ the IP we brought in for the SHA 1 hash used in the design containing potentially malicious code. This is addressed by combing through files and testing of module to ensure no risk to our design.

### **Conclusion:**

$\bullet$

•

inst.reg\_sha\_address[7]=0 st0.core.digest update=(

.shal inst0.core.ready=1 st.shal inst0.init new=0 nst.shal\_inst0.next\_new=0 st.shal\_inst0.ready\_reg=: sha1\_ctrl\_inst.state[1] =1 sha1\_ctrl\_inst.state[2]=0 sha1\_ctrl\_inst.state[3] =0 shal ctrl inst.state[4]=0

- All tests & requirements pass

- Submitted to eFabless

- Ready for manufacturing

| fables | S Projects ~        | Tools ~ Marketpl   | ace ~ Community ~ | Company ~             |           |   |

|--------|---------------------|--------------------|-------------------|-----------------------|-----------|---|

| IPW-7  | Open MPW            |                    |                   |                       |           |   |

|        |                     |                    |                   |                       |           |   |

|        | Details Summary     | Projects (105)     | Announcements (2) | Manage My Submissions |           |   |

|        | Bitcoin Mining Asic | Add another projec | et to Shuttle 🕂   |                       |           |   |

|        | View Project 🎓      |                    |                   |                       |           |   |

|        | MPW Precheck        |                    | Complete 🥪        |                       | Re-Submit | ^ |

|        | Tapeout             |                    | Complete 🤗        |                       | Re-Submit | ^ |

|        | Shipping Addre      | ess                | Complete 🥪        |                       | Edit      | ^ |

|        | Legal               |                    | Complete 🥪        |                       |           | ^ |

|        | Submission          |                    | In Review 🔗       |                       | Cancel    | ^ |

|        |                     |                    |                   |                       |           |   |

•

Manpower - A lot